前言

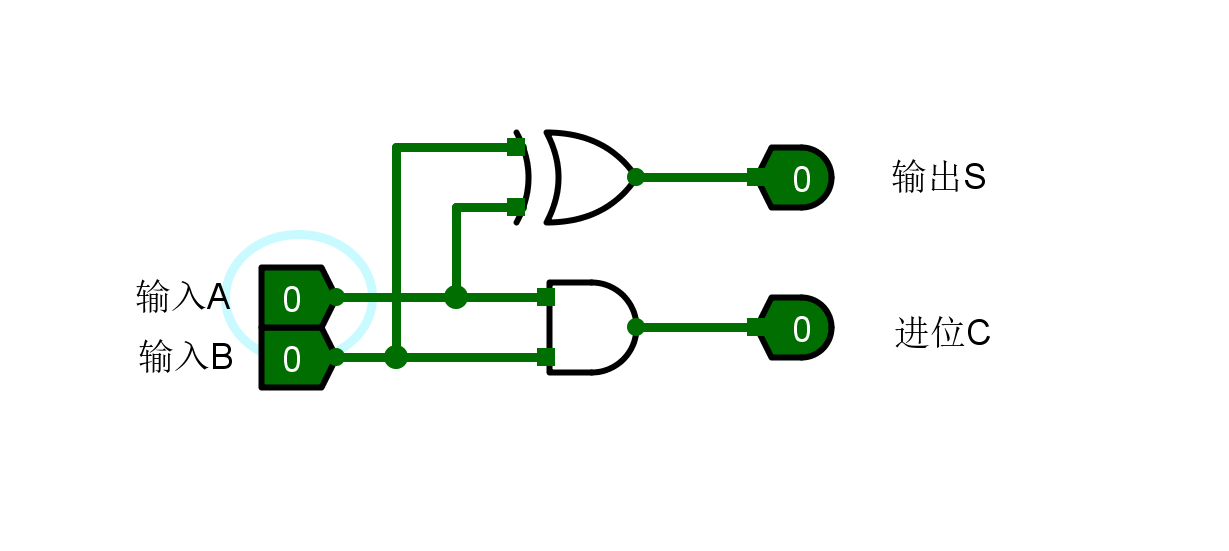

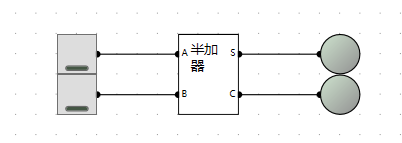

半加器

半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。 是实现两个一位二进制数的加法运算电路。

实现原理

结果S是AB的异或 进位C是AB的与

$$

S = \overline{A}B + \overline{B}A

$$

$$

C = AB

$$

真值表:

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

电路实现:

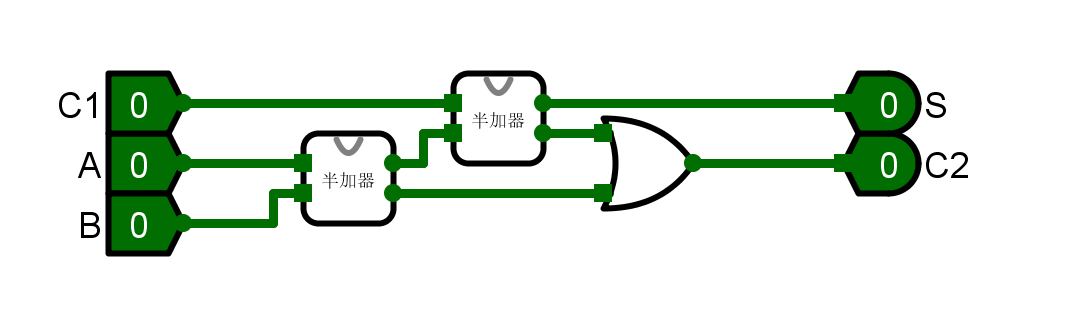

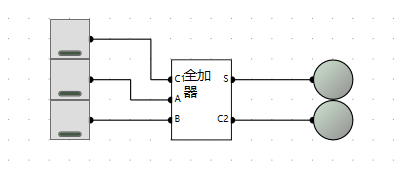

全加器

门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。

实现原理

$$

S_i = A_i \bigoplus B_i\bigoplus C_{i-1}

$$

$$

C_i=A_iC_i+A_iB_i+B_iC_{i-1}

$$

真值表:

| C1 | A | B | S | C2 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

电路实现:

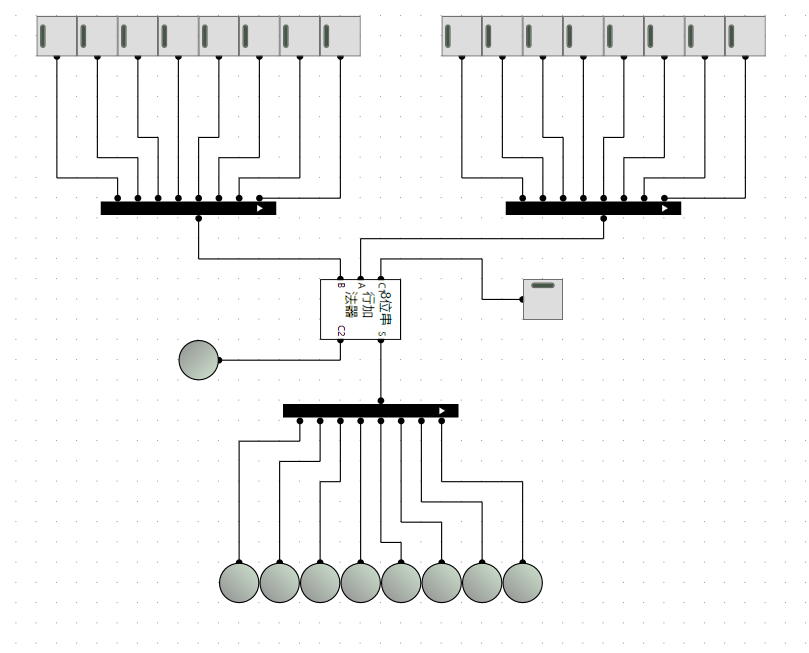

8位串行加法器